## **EVB PCB Schematics and Pinouts**

The SPU-001 EVB PCB can be used with any host with an SPI interface and 1.8-3.3V logic. There are two variations available:

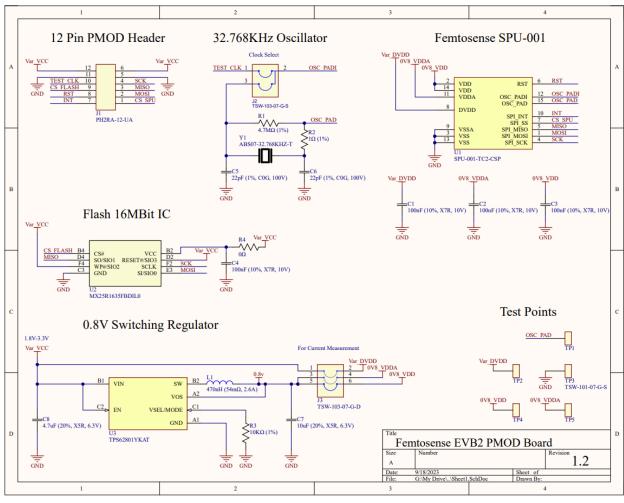

- EVB2: SPU-001-CSP (TC2) package

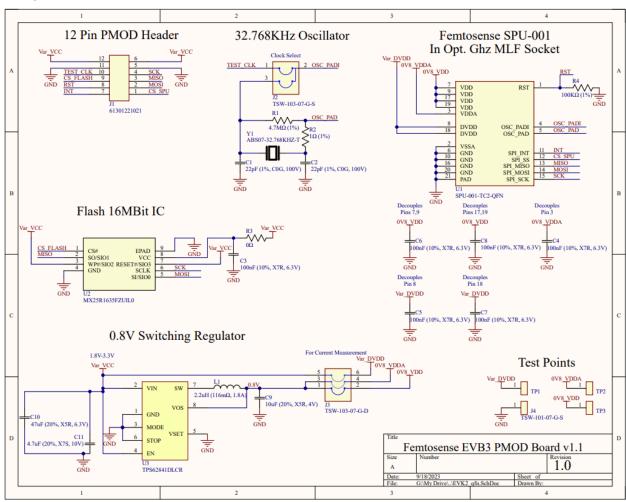

- EVB3: SPU-001-QFN (TC2) package

- EVB4: SPU-001-CSP (Mass Production) package

These boards are mostly backwards compatible, however EVB4 replaces one VCC pin with the 0.8V regulator enable pin. The schematics are given below:

#### EVB2

#### EVB3

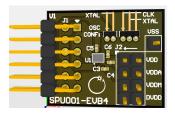

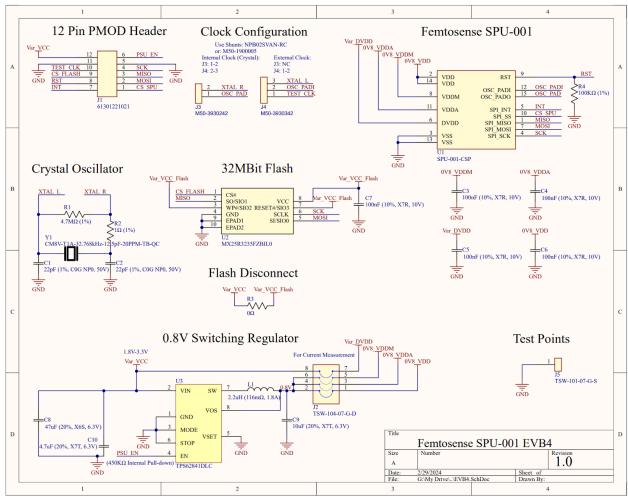

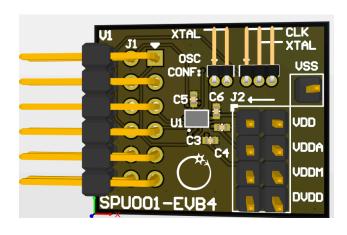

#### EVB4

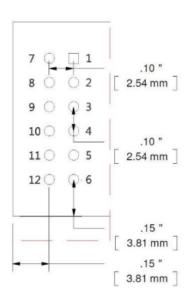

The pinout of the main header J1 is pin-compatible with the Digilent PMOD interface type 2A specification. Optionally, on EVB4, the 0.8v regulator output can be controlled.

| Pin | Description                            | Note                                |

|-----|----------------------------------------|-------------------------------------|

| 1   | SPI Chip Select for SPU-001            | active low                          |

| 2   | SPI MOSI signal                        | mode 0                              |

| 3   | SPI MISO signal                        | mode 0                              |

| 4   | SPI SCK clock signal                   | mode 0                              |

| 5   | Ground                                 |                                     |

| 6   | PSU Enable (EVB4) or VCC (EVB2, EVB3)  | active high                         |

| 7   | SPU Interrupt signal                   | logic high when data frame is ready |

| 8   | SPU Reset signal                       | active high                         |

| 9   | SPI Chip Select for onboard flash chip | active low                          |

| 10  | Reference Clock for SPU                | VCC level                           |

| 11  | Ground                                 |                                     |

| 12  | vcc                                    | 1.8V-3.3V                           |

Note: All IO, including PSU enable and the reference clock, should be referenced to VCC logic level.

## **Jumpers**

The jumpers should be configured as follows:

| Pin                              | Description               | Configuration                                                                                                                    |

|----------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| DVDD                             | IO power rail, VCC        | connect jumper vertically (EVB2) or horizontally (EVB3,EVB4)                                                                     |

| VDDA                             | PLL power rail, 0.8v      | connect jumper vertically (EVB2) or horizontally (EVB3,EVB4)                                                                     |

| VDDM                             | Memory power rail, 0.8v   | connect jumper horizontally (EVB4)                                                                                               |

| VDD                              | Main power rail, 0.8v     | connect jumper vertically (EVB2) or horizontally (EVB3,EVB4)                                                                     |

| CLK_SEL<br>(EVB2,EVB3)           | Reference clock selector  | INT position: onboard oscillator<br>EXT position: reference clock from J1 pin 10                                                 |

| OSC CONF<br>(EVB4,<br>2 jumpers) | Reference clock selectors | For onboard oscillator: place 2 jumpers across XTAL markers For reference clock from J1 pin 10: place 1 jumper across CLK marker |

# Change Log

| Version | Release Date | Description                 |

|---------|--------------|-----------------------------|

| 1.0     | 2023-05-04   | Initial release             |

| 1.1     | 2023-07-23   | Updated schematic with typo |

| 1.2     | 2023-09-18   | Added EVB3                  |

| 1.3     | 2024-02-29   | Added EVB4                  |